Definition of n-well area 2. Wells at same potential 0λ 4.

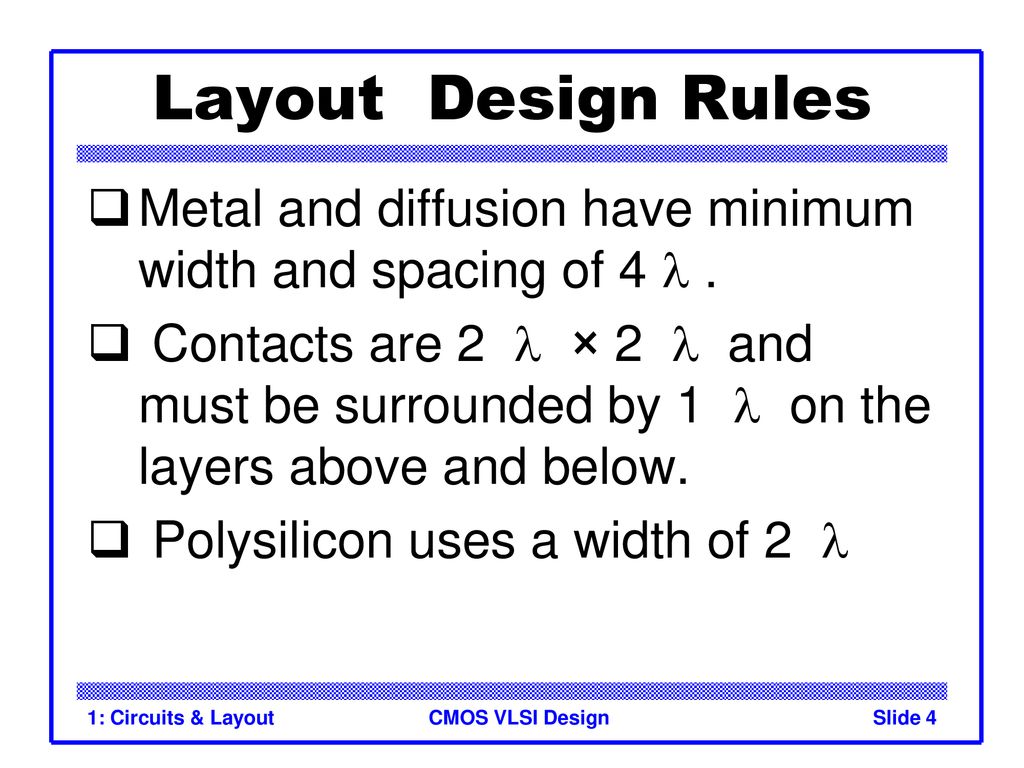

Arrows between objects denote a minimum spacing and arrows showing the size of an object denote a minimum width.

. 23 CMOS Design Rules. Metal to active Via. VDD contact to substrate.

Cross-Section of CMOS Technology Design Rules Interface between designer and process engineer Guidelines for constructing process masks Unit dimension. Layout and Rules Reasons behind Rules. I These rules are the designers interface to the fabrication process.

Does show all components vias except possibly tub ties relative placement. Rule 31 for example is the minimum width of poly 2 l. Diffusion and Tap Width and Space Martin p44 Cypress nwell Diff-tap poly Pdiff Minimum width.

Use of S to denote source. Definition of source and drains regions for the NMOS and PMOS. The MOSIS design rules are as follows.

1 Rules for N-well as shown in Figure below. Worlds Best PowerPoint Templates - CrystalGraphics offers more PowerPoint templates than anyone else in the world with over 4 million to choose from. The opposite is true for p-well CMOS technology see Fig.

Threshold implant of two types of transistor 3. Metalpattern omitted for clarity VSS contact to P-well. DESIGN RULES AND LAYOUT.

How to build your own simple CMOS chip CMOS transistors Building logic gates from transistors Transistor layout and fabrication Rest of the course. VLSI CIRCUIT DESIGN PROCESS. Worlds Best PowerPoint Templates - CrystalGraphics offers more PowerPoint templates than anyone else in the world with over 4 million to choose from.

Theyll give your presentations a professional memorable appearance - the kind of sophisticated look that. N diff Poly P diff Contacts Metal P Substrate N Well. The MOSIS rules are scalable λ rules.

3 Must be wide enough to enclose a contact. Minimum width 10λ 2. Diffusion for all transistors in a row With poly vertical All gates include well and substrate.

Each of the rule numbers may have different values for different manufacturers. Lambda Based Design Rules. 9 CMOS VLSI Design Standard Cell Layout Layout Slide 17 Layout CMOS VLSI Design Slide 18 Gate Layout Standard cell design methodology VDD and GND should be some standard height parallel Within cell all pMOS in top half and all nMOS in bottom half Preferred practice.

CMOS VLSI Design The rules describe the minimum width to avoid breaks in a line minimum spacing to avoid shorts between lines and minimum overlap to ensure that two layers completely overlap. 2 Rules for CMOS layout Similar to those for NMOS except No 1. How to build a good CMOS chip 0.

It is isolated from the substrate and thus can be connected to the source. For n-well CMOS process the bulk of the PMOS is the n-well. Layout Design rules Lambda CMOS Layout.

1. The USP of the NPTEL courses is its flexibility. P-well and P mask rules.

Sketch a 4-input CMOS NOR gate Complementary CMOS Complementary CMOS logic gates nMOS pull-down network pMOS pull-up network aka. Introduction Silicon Lattice Transistors are built on a silicon substrate Silicon. Particular rules for P-well CMOS process VDD and VSS contacts P-well.

Design rules can be absolute measurements eg. Theyll give your presentations a professional memorable appearance - the kind of sophisticated look that. The courses are so well structured that attendees can select parts of any lecture that are specifically useful for them.

Gate source drain and substrate body Complementary MOS CMOS Using two types of MOSFETs to create logic networks NMOS PMOS. On the other hand the bulk of the NMOS is the substrate itself and thus the bulk of the NMOS cant be connected to the. 1 Peak doping concentration needs to be repeatable independent of width or the lateral diffusion 2 Photoresist must have a minimum opening to allow the implant.

Minimum line width scalable design rules. Wells at same potential with spacing 6λ 3. In nm or scaled to an abstract unit the lambda.

Missing electron called hole p-type nMOS Operation Body is commonly tied. Winner of the Standing Ovation Award for Best PowerPoint Templates from Presentations Magazine. Wells of different type spacing 8λ 2 Rules for Active area shown in Figure below.

For working professionals the lectures are a boon. Design rules based on single parameter λ. Does not show exact placement transistor sizes wire lengths wire widths tub boundaries.

Design rules I The geometric design rules are a contract between the foundry and the designer. Winner of the Standing Ovation Award for Best PowerPoint Templates from Presentations Magazine. Metal-Oxide-Semiconductor Field-Effect Transistor N-type MOS NMOS and P-type MOS PMOS Voltage-controlled switches A MOSFET has four terminals.

In a 06 µm process this corresponds to an actual width of 12 µm and a length of 06 µm. Layout Design rules Lambda Same N and P alters symmetry L min Wpmos2 Wnmos. Circuits Layout A Brief History 1958.

Rules for CMOS layout. To ensure the separation of the PMOS and NMOS devices. Extra electron n-type Group III.

First integrated circuit Flip-flop using two transistors Built by Jack Kilby at Texas Instruments 2010 Intel Core i7. Register for exams Timelines and Guidelines Course Booklet Part 1 Part 2 Part 3 Part 4. Lambda parameter absolute dimensions micron rules CMOS Process Layers Intra-Layer Design Rules Transistor Layout Vias and.

Figure 211 defines the design rules for a CMOS process using pictures. 6884 Spring 2005 2072005 L03 CMOS Technology 12. Lambda-based designs are scaled to the appropriate absolute units depending on the manufacturing process finally used.

Layer Representations Substrates andor Wells Diffusion Regions Active areas Select regions. Complementary Metal Oxide Semiconductor Fast cheap low power transistors Today. Split contacts may also be made with separate cuts.

Overview Physical principles Combinational logic Sequential logic Datapath Memories Trends Dopants Silicon is a semiconductor Pure silicon has no free carriers and conducts poorly Adding dopants increases the conductivity Group V. I They guarantee that the transfers onto the wafer preserve the topology and geometry of the patterns. Simple for the designer.

To direct and control logic signals in IC design MOSFET. Sketch a 4-input CMOS NAND gate CMOS Gate Design Activity. A stick diagram is a cartoon of a layout.

Transistor dimensions are often specified by their WidthLength WL ratio. Width of pMOS should be twice the width of nMOS. For contacts to substrate or well Polysilicon Layers Metal Interconnects Contact.

Minimum spacing 3λ 3. Minimum separations minimum and maximum widths overlap rules. Design Circuits Layout Outline CMOS Gate Design Pass Transistors CMOS Latches Flip-Flops Standard Cell Layouts Stick Diagrams CMOS Gate Design Activity.

P mask 2 2 cut on 4 4 overlap area. Minimum width 3λ 2. Circuits Layout Outline A Brief History CMOS Gate Design Pass Transistors CMOS Latches Flip-Flops Standard Cell Layouts Stick Diagrams 1.

Layout Design Rules 2 Introduction Layout Rules Is Also Referred As Design Rules It Is Considered As A Prescription For Preparing Photomasks Ppt Download

Layout Design Rules 2 Introduction Layout Rules Is Also Referred As Design Rules It Is Considered As A Prescription For Preparing Photomasks Ppt Download

Cmos Design Rules And Packaging Electronic Systems 2017 Youtube

Module 3 Mos Designs Stick Diagrams Designrules Ppt Video Online Download

Layout Design Rules 2 Introduction Layout Rules Is Also Referred As Design Rules It Is Considered As A Prescription For Preparing Photomasks Ppt Download

Vlsi Design Cmos Layout Ppt Download

0 comments

Post a Comment